## System V Application Binary Interface AMD64 Architecture Processor Supplement Draft Version 0.99.7

Edited by Michael Matz<sup>1</sup>, Jan Hubička<sup>2</sup>, Andreas Jaeger<sup>3</sup>, Mark Mitchell<sup>4</sup>

November 17, 2014

<sup>&</sup>lt;sup>1</sup>matz@suse.de

<sup>&</sup>lt;sup>2</sup>jh@suse.cz

<sup>&</sup>lt;sup>3</sup>aj@suse.de

<sup>&</sup>lt;sup>4</sup>mark@codesourcery.com

# **Contents**

| 1                                                                                                                                                                                                                                                                                                                                                                                             | Intr               | oductio    | n                                      | 8  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------|----------------------------------------|----|

| 2                                                                                                                                                                                                                                                                                                                                                                                             | Soft               | stallation | 9                                      |    |

| 2 Software Installatio 3 Low Level System I 3.1 Machine Interfa 3.1.1 Process 3.1.2 Data Re 3.2 Function Callin 3.2.1 Registe 3.2.2 The Sta 3.2.3 Parame 3.3 Operating Syste 3.3.1 Except 3.3.2 Virtual 3.3.3 Page Si 3.3.4 Virtual 3.4 Process Initialia 3.4.1 Initial Si 3.4.2 Thread 3.4.3 Auxilia 3.5 Coding Examp 3.5.1 Archite 3.5.2 Convert 3.5.3 Position 3.5.4 Data O 3.5.5 Function | System Information | 10         |                                        |    |

|                                                                                                                                                                                                                                                                                                                                                                                               | 3.1                | Machin     | ne Interface                           | 10 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.1.1      | Processor Architecture                 | 10 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.1.2      | Data Representation                    | 10 |

|                                                                                                                                                                                                                                                                                                                                                                                               | 3.2                | Function   | on Calling Sequence                    | 13 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.2.1      | Registers and the Stack Frame          | 14 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.2.2      | The Stack Frame                        | 15 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.2.3      | Parameter Passing                      | 16 |

|                                                                                                                                                                                                                                                                                                                                                                                               | 3.3                | Operat     | ing System Interface                   | 23 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.3.1      | Exception Interface                    | 23 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.3.2      | Virtual Address Space                  | 23 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.3.3      | Page Size                              | 23 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.3.4      | Virtual Address Assignments            | 23 |

| 3.3 Operating System Interface 3.3.1 Exception Interface 3.3.2 Virtual Address Space 3.3.3 Page Size 3.3.4 Virtual Address Assignments 3.4 Process Initialization 3.4.1 Initial Stack and Register State 3.4.2 Thread State                                                                                                                                                                   |                    | 26         |                                        |    |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    |            |                                        | 26 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.4.2      | Thread State                           | 29 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.4.3      | Auxiliary Vector                       | 29 |

|                                                                                                                                                                                                                                                                                                                                                                                               | 3.5                | Coding     | g Examples                             | 31 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | _          | Architectural Constraints              | 32 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.5.2      | Conventions                            | 34 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.5.3      | Position-Independent Function Prologue | 35 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.5.4      | Data Objects                           | 36 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.5.5      | Function Calls                         | 44 |

|                                                                                                                                                                                                                                                                                                                                                                                               |                    | 3.5.6      | Branching                              | 46 |

|   |      | 3.5.7        | Variable Argument Lists              | 49       |

|---|------|--------------|--------------------------------------|----------|

|   | 3.6  | DWAF         | RF Definition                        | 54       |

|   |      | 3.6.1        | DWARF Release Number                 |          |

|   |      | 3.6.2        | DWARF Register Number Mapping        | 55       |

|   | 3.7  | Stack        | Unwind Algorithm                     | 55       |

| 4 | Obj  | ect Files    | s                                    | 59       |

|   | 4.1  | ELF H        | Ieader                               | 59       |

|   |      | 4.1.1        | Machine Information                  | 59       |

|   |      | 4.1.2        | Number of Program Headers            | 59       |

|   | 4.2  | Section      | ns                                   | 60       |

|   |      | 4.2.1        | Section Flags                        | 60       |

|   |      | 4.2.2        | Section types                        | 61       |

|   |      | 4.2.3        | Special Sections                     | 61       |

|   |      | 4.2.4        | EH_FRAME sections                    | 62       |

|   | 4.3  | Symbo        | ol Table                             | 67       |

|   | 4.4  | -            | ation                                | 68       |

|   |      | 4.4.1        | Relocation Types                     | 68       |

|   |      | 4.4.2        | Large Models                         | 73       |

| 5 | Prog | eram Lo      | oading and Dynamic Linking           | 74       |

|   | 5.1  | -            | um Loading                           | 74       |

|   |      | 5.1.1        | Program header                       | 75       |

|   | 5.2  |              | nic Linking                          | 75       |

|   |      | 5.2.1        | Program Interpreter                  | 82       |

|   |      | 5.2.2        |                                      | 82       |

| 6 | Libr | aries        |                                      | 83       |

| U | 6.1  |              | ary                                  | 83       |

|   | 0.1  | 6.1.1        | Global Data Symbols                  |          |

|   |      | 6.1.2        | Floating Point Environment Functions | 83       |

|   | 6.2  |              | ad Library Interface                 | 84       |

|   | 0.2  | 6.2.1        | Exception Handler Framework          | 85       |

|   |      | 6.2.2        | Data Structures                      | 87       |

|   |      | 6.2.3        | Throwing an Exception                | 89       |

|   |      | 6.2.4        |                                      | 92       |

|   |      | 6.2.5        | Exception Object Management          |          |

|   |      | 6.2.6        | Context Management                   | 92<br>95 |

|   |      | O. $Z$ . $O$ | ECINOHALITY NORTHE                   | 97       |

|   | 6.3  | Unwin    | ding Through Assembler Code     | . 99 |

|---|------|----------|---------------------------------|------|

| 7 | Deve | elopmer  | nt Environment                  | 102  |

| 8 | Exec | cution E | Environment                     | 103  |

| 9 | Con  | ventions | S                               | 104  |

|   | 9.1  | C++ .    |                                 | 105  |

|   | 9.2  | Fortrar  | 1                               | 106  |

|   |      | 9.2.1    | Names                           | 106  |

|   |      | 9.2.2    | Representation of Fortran Types |      |

|   |      | 9.2.3    | Argument Passing                |      |

|   |      | 9.2.4    | Functions                       |      |

|   |      | 9.2.5    | COMMON blocks                   |      |

|   |      | 9.2.6    | Intrinsics                      | 111  |

| A | Linu | ıx Conv  | rentions                        | 122  |

|   | A.1  | Execut   | ion of 32-bit Programs          | 122  |

|   | A.2  | AMD6     | 64 Linux Kernel Conventions     | 122  |

|   |      | A.2.1    | Calling Conventions             | 122  |

|   |      | A.2.2    |                                 |      |

|   |      | A.2.3    | Required Processor Features     |      |

|   |      | A 2.4    | Miscellaneous Remarks           | 123  |

# **List of Tables**

| 3.1  | Hardware Exceptions and Signals                         |

|------|---------------------------------------------------------|

| 3.2  | Floating-Point Exceptions                               |

| 3.3  | x87 Floating-Point Control Word                         |

| 3.4  | MXCSR Status Bits                                       |

| 3.5  | rflags Bits 27                                          |

| 4.1  | AMD64 Identification                                    |

| 4.2  | AMD64 Specific Section Header Flag, sh_flags 60         |

| 4.3  | Section Header Types 61                                 |

| 4.4  | Special sections 61                                     |

| 4.5  | Additional Special Sections for the Large Code Model 62 |

| 4.6  | Common Information Entry (CIE)                          |

| 4.7  | CIE Augmentation Section Content                        |

| 4.8  | Frame Descriptor Entry (FDE)                            |

| 4.9  | FDE Augmentation Section Content 67                     |

| 4.10 | Relocation Types                                        |

| 4.11 |                                                         |

| 5.1  | Program Header Types                                    |

| 7.1  | Predefined Pre-Processor Symbols                        |

| 9.1  | Mil intrinsics                                          |

| 9.2  | F77 intrinsics                                          |

| 9.3  | F90 intrinsics                                          |

| 9.4  | Math intrinsics                                         |

| 9.5  | Unix intrinsics                                         |

| A.1  | Required Processor Features                             |

# **List of Figures**

| 3.1  | Scalar Types                                                 | 11 |

|------|--------------------------------------------------------------|----|

| 3.2  | Bit-Field Ranges                                             | 13 |

| 3.3  | Stack Frame with Base Pointer                                | 15 |

| 3.4  | Register Usage                                               | 20 |

| 3.5  | Parameter Passing Example                                    | 22 |

| 3.6  | Register Allocation Example                                  | 22 |

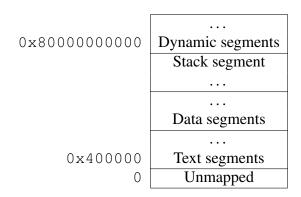

| 3.7  | Virtual Address Configuration                                | 25 |

| 3.8  | Conventional Segment Arrangements                            | 26 |

| 3.9  | Initial Process Stack                                        | 28 |

| 3.10 | auxv_t Type Definition                                       | 29 |

| 3.11 | Auxiliary Vector Types                                       | 30 |

| 3.12 | Position-Independent Function Prolog Code                    | 35 |

| 3.13 | Absolute Load and Store (Small Model)                        | 37 |

| 3.14 | Position-Independent Load and Store (Small PIC Model)        | 38 |

| 3.15 | Absolute Load and Store (Medium Model)                       | 39 |

| 3.16 | Position-Independent Load and Store (Medium PIC Model)       | 40 |

| 3.17 | Position-Independent Load and Store (Medium PIC Model), con- |    |

|      | tinued                                                       | 41 |

| 3.18 | Absolute Global Data Load and Store                          | 42 |

| 3.19 | Faster Absolute Global Data Load and Store                   | 42 |

| 3.20 | Position-Independent Global Data Load and Store              | 43 |

| 3.21 | Faster Position-Independent Global Data Load and Store       | 43 |

| 3.22 | Position-Independent Direct Function Call (Small and Medium  |    |

|      | Model)                                                       | 44 |

|      | Position-Independent Indirect Function Call                  | 44 |

| 3.24 | Absolute Direct and Indirect Function Call                   | 45 |

|      | Position-Independent Direct and Indirect Function Call       | 45 |

| 3.26 | Absolute Branching Code                                      | 47 |

| 3.27 | Implicit Calculation of Target Address                 | 47  |

|------|--------------------------------------------------------|-----|

| 3.28 | Position-Independent Branching Code                    | 48  |

|      | Absolute Switch Code                                   | 48  |

|      | Position-Independent Switch Code                       | 49  |

| 3.31 | Parameter Passing Example with Variable-Argument List  | 50  |

| 3.32 | Register Allocation Example for Variable-Argument List | 50  |

| 3.33 | Register Save Area                                     | 51  |

| 3.34 | va_list Type Declaration                               | 52  |

| 3.35 | Sample Implementation of va_arg(1, int)                | 54  |

| 3.36 | DWARF Register Number Mapping                          | 56  |

|      | Pointer Encoding Specification Byte                    | 57  |

| 4.1  | Relocatable Fields                                     | 68  |

| 5.1  | Global Offset Table                                    | 76  |

| 5.2  | Procedure Linkage Table (small and medium models)      | 78  |

| 5.3  | Final Large Code Model PLT                             | 81  |

| 6.1  | Examples for Unwinding in Assembler                    | 101 |

| 9.1  | Example mapping of names                               | 107 |

| 9.2  | Mapping of Fortran to C types                          |     |

## **Revision History**

- **0.99** Add description of TLS relocations (thanks to Alexandre Oliva) and mention the decimal floating point and AVX types (thanks to H.J. Lu).

- 0.98 Various clarifications and fixes according to feedback from Sun, thanks to Terrence Miller. DWARF register numbers for some system registers, thanks to Jan Beulich. Add R\_X86\_64\_SIZE32 and R\_X86\_64\_SIZE64 relocations; extend meaning of e\_phnum to handle more than 0xffff program headers, thanks to Rod Evans. Add footnote about passing of decimal datatypes. Specify that \_Bool is booleanized at the caller.

- **0.97** Integrate Fortran ABI.

- **0.96** Use SHF\_X86\_64\_LARGE instead SHF\_AMD64\_LARGE (thanks to Evandro Menezes). Correct various grammatical errors noted by Mark F. Haigh,

- who also noted that there are no global VLAs in C99. Thanks also to Robert R. Henry.

- **0.95** Include description of the medium PIC memory model (thanks to Jan Hubička) and large model (thanks to Evandro Menezes).

- **0.94** Add sections in Development Environment, Program Loading, a description of EH\_FRAME sections and general cleanups to make text in this ABI self-contained. Thanks to Michael Walker and Terrence Miller.

- **0.93** Add sections about program headers, new section types and special sections for unwinding information. Thanks to Michael Walker.

- **0.92** Fix some typos (thanks to Bryan Ford), add section about stack layout in the Linux kernel. Fix example in figure 3.5 (thanks to Tom Horsley). Add section on unwinding through assembler (written by Michal Ludvig). Remove mmxext feature (thanks to Evandro Menezes). Add section on Fortran (by Steven Bosscher) and stack unwinding (by Jan Hubička).

- **0.91** Clarify that x87 is default mode, not MMX (by Hans Peter Anvin).

- 0.90 Change DWARF register numbers again; mention that \_\_\_m128 needs alignment; fix typo in figure 3.3; add some comments on kernel expectations; mention TLS extensions; add example for passing of variable-argument lists; change semantics of %rax in variable-argument lists; improve formatting; mention that X87 class is not used for passing; make /lib64 a Linux specific section; rename x86-64 to AMD64; describe passing of complex types. Special thanks to Andi Kleen, Michal Ludvig, Michael Matz, David O'Brien and Eric Young for their comments.

- **0.21** Define \_\_int128 as class INTEGER in register passing. Mention that %al is used for variadic argument lists. Fix some textual problems. Thanks to H. Peter Anvin, Bo Thorsen, and Michael Matz.

- 0.20 2002-07-11 Change DWARF register number values of %rbx, %rsi, %rsi (thanks to Michal Ludvig). Fix footnotes for fundamental types (thanks to H. Peter Anvin). Specify size\_t (thanks to Bo Thorsen and Andreas Schwab). Add new section on floating point environment functions.

**0.19** — **2002-03-27** Set name of Linux dynamic linker, mention %fs. Incorporate changes from H. Peter Anvin <hpa@zytor.com> for booleans and define handling of sub-64-bit integer types in registers.

## Chapter 1

## Introduction

The AMD64<sup>1</sup> architecture<sup>2</sup> is an extension of the x86 architecture. Any processor implementing the AMD64 architecture specification will also provide compatibility modes for previous descendants of the Intel 8086 architecture, including 32-bit processors such as the Intel 386, Intel Pentium, and AMD K6-2 processor. Operating systems conforming to the AMD64 ABI may provide support for executing programs that are designed to execute in these compatibility modes. The AMD64 ABI does not apply to such programs; this document applies only to programs running in the "long" mode provided by the AMD64 architecture.

Except where otherwise noted, the AMD64 architecture ABI follows the conventions described in the Intel386 ABI. Rather than replicate the entire contents of the Intel386 ABI, the AMD64 ABI indicates only those places where changes have been made to the Intel386 ABI.

No attempt has been made to specify an ABI for languages other than C. However, it is assumed that many programming languages will wish to link with code written in C, so that the ABI specifications documented here apply there too.<sup>3</sup>

<sup>&</sup>lt;sup>1</sup>AMD64 has been previously called x86-64. The latter name is used in a number of places out of historical reasons instead of AMD64.

<sup>&</sup>lt;sup>2</sup>The architecture specification is available on the web at http://www.x86-64.org/documentation.

<sup>&</sup>lt;sup>3</sup>See section 9.1 for details on C++ ABI.

# **Chapter 2**

## **Software Installation**

This document does not specify how software must be installed on an AMD64 architecture machine.

## Chapter 3

## **Low Level System Information**

### 3.1 Machine Interface

#### 3.1.1 Processor Architecture

### 3.1.2 Data Representation

Within this specification, the term *byte* refers to a 8-bit object, the term *twobyte* refers to a 16-bit object, the term *fourbyte* refers to a 32-bit object, the term *eight-byte* refers to a 64-bit object, and the term *sixteenbyte* refers to a 128-bit object.

#### **Fundamental Types**

Figure 3.1 shows the correspondence between ISO C's scalar types and the processor's. \_\_\_int128, \_\_\_float128, \_\_\_m64, \_\_\_m128 and \_\_\_m256 types are optional.

The \_\_float128 type uses a 15-bit exponent, a 113-bit mantissa (the high order significant bit is implicit) and an exponent bias of 16383.<sup>2</sup>

The long double type uses a 15 bit exponent, a 64-bit mantissa with an explicit high order significant bit and an exponent bias of 16383.<sup>3</sup> Although a long

<sup>&</sup>lt;sup>1</sup>The Intel386 ABI uses the term *halfword* for a 16-bit object, the term *word* for a 32-bit object, the term *doubleword* for a 64-bit object. But most IA-32 processor specific documentation define a *word* as a 16-bit object, a *doubleword* as a 32-bit object, a *quadword* as a 64-bit object and a *double quadword* as a 128-bit object.

<sup>&</sup>lt;sup>2</sup>Initial implementations of the AMD64 architecture are expected to support operations on the \_float128 type only via software emulation.

<sup>&</sup>lt;sup>3</sup>This type is the x87 double extended precision data type.

Figure 3.1: Scalar Types

|           |                              |        | Alignment | AMD64                       |

|-----------|------------------------------|--------|-----------|-----------------------------|

| Type      | C                            | sizeof | (bytes)   | Architecture                |

|           | _Bool <sup>†</sup>           | 1      | 1         | boolean                     |

|           | char                         | 1      | 1         | signed byte                 |

|           | signed char                  |        |           |                             |

|           | unsigned char                | 1      | 1         | unsigned byte               |

|           | short                        | 2      | 2         | signed twobyte              |

|           | signed short                 |        |           |                             |

|           | unsigned short               | 2      | 2         | unsigned twobyte            |

|           | int                          | 4      | 4         | signed fourbyte             |

| Integral  | signed int                   |        |           |                             |

|           | enum <sup>†††</sup>          |        |           |                             |

|           | unsigned int                 | 4      | 4         | unsigned fourbyte           |

|           | long                         | 8      | 8         | signed eightbyte            |

|           | signed long                  |        |           |                             |

|           | long long                    |        |           |                             |

|           | signed long long             |        |           |                             |

|           | unsigned long                | 8      | 8         | unsigned eightbyte          |

|           | unsigned long long           | 8      | 8         | unsigned eightbyte          |

|           | int128 <sup>††</sup>         | 16     | 16        | signed sixteenbyte          |

|           | signedint128 <sup>††</sup>   | 16     | 16        | signed sixteenbyte          |

|           | unsignedint128 <sup>††</sup> | 16     | 16        | unsigned sixteenbyte        |

| Pointer   | any-type *                   | 8      | 8         | unsigned eightbyte          |

|           | any-type (*)()               |        |           |                             |

| Floating- | float                        | 4      | 4         | single (IEEE-754)           |

| point     | double                       | 8      | 8         | double (IEEE-754)           |

|           | long double                  | 16     | 16        | 80-bit extended (IEEE-754)  |

|           | float128 <sup>††</sup>       | 16     | 16        | 128-bit extended (IEEE-754) |

| Decimal-  | _Decimal32                   | 4      | 4         | 32bit BID (IEEE-754R)       |

| floating- | _Decimal64                   | 8      | 8         | 64bit BID (IEEE-754R)       |

| point     | _Decimal128                  | 16     | 16        | 128bit BID (IEEE-754R)      |

| Packed    | m64 <sup>††</sup>            | 8      | 8         | MMX and 3DNow!              |

|           | m128 <sup>††</sup>           | 16     | 16        | SSE and SSE-2               |

|           | m256 <sup>††</sup>           | 32     | 32        | AVX                         |

<sup>†</sup> This type is called bool in C++.

<sup>††</sup> These types are optional.

<sup>†††</sup> C++ and some implementations of C permit enums larger than an int. The underlying type is bumped to an unsigned int, long int or unsigned long int, in that order.

double requires 16 bytes of storage, only the first 10 bytes are significant. The remaining six bytes are tail padding, and the contents of these bytes are undefined.

The \_\_int128 type is stored in little-endian order in memory, i.e., the 64 low-order bits are stored at a a lower address than the 64 high-order bits.

A null pointer (for all types) has the value zero.

The type size\_t is defined as unsigned long.

Booleans, when stored in a memory object, are stored as single byte objects the value of which is always 0 (false) or 1 (true). When stored in integer registers (except for passing as arguments), all 8 bytes of the register are significant; any nonzero value is considered true.

Like the Intel386 architecture, the AMD64 architecture in general does not require all data accesses to be properly aligned. Misaligned data accesses are slower than aligned accesses but otherwise behave identically. The only exceptions are that \_\_m128 and \_\_m256 must always be aligned properly.

#### **Aggregates and Unions**

Structures and unions assume the alignment of their most strictly aligned component. Each member is assigned to the lowest available offset with the appropriate alignment. The size of any object is always a multiple of the object's alignment.

An array uses the same alignment as its elements, except that a local or global array variable of length at least 16 bytes or a C99 variable-length array variable always has alignment of at least 16 bytes.<sup>4</sup>

Structure and union objects can require padding to meet size and alignment constraints. The contents of any padding is undefined.

#### **Bit-Fields**

C struct and union definitions may include bit-fields that define integral values of a specified size.

The ABI does not permit bit-fields having the type \_\_m64, \_\_m128 or \_\_m256. Programs using bit-fields of these types are not portable.

Bit-fields that are neither signed nor unsigned always have non-negative values. Although they may have type char, short, int, or long (which can have neg-

<sup>&</sup>lt;sup>4</sup>The alignment requirement allows the use of SSE instructions when operating on the array. The compiler cannot in general calculate the size of a variable-length array (VLA), but it is expected that most VLAs will require at least 16 bytes, so it is logical to mandate that VLAs have at least a 16-byte alignment.

Figure 3.2: Bit-Field Ranges

| Bit-field Type | Width $\boldsymbol{w}$ | Range                     |  |

|----------------|------------------------|---------------------------|--|

| signed char    |                        | $-2^{w-1}$ to $2^{w-1}-1$ |  |

| char           | 1 to 8                 | 0 to $2^{w} - 1$          |  |

| unsigned char  |                        | $0 \text{ to } 2^w - 1$   |  |

| signed short   |                        | $-2^{w-1}$ to $2^{w-1}-1$ |  |

| short          | 1 to 16                | 0 to $2^{w} - 1$          |  |

| unsigned short |                        | 0 to $2^{w} - 1$          |  |

| signed int     |                        | $-2^{w-1}$ to $2^{w-1}-1$ |  |

| int            | 1 to 32                | 0 to $2^{w} - 1$          |  |

| unsigned int   |                        | 0 to $2^{w} - 1$          |  |

| signed long    |                        | $-2^{w-1}$ to $2^{w-1}-1$ |  |

| long           | 1 to 64                | 0 to $2^{w} - 1$          |  |

| unsigned long  |                        | $0 \text{ to } 2^w - 1$   |  |

ative values), these bit-fields have the same range as a bit-field of the same size with the corresponding unsigned type. Bit-fields obey the same size and alignment rules as other structure and union members.

Also:

- bit-fields are allocated from right to left

- bit-fields must be contained in a storage unit appropriate for its declared type

- bit-fields may share a storage unit with other struct / union members

Unnamed bit-fields' types do not affect the alignment of a structure or union.

## 3.2 Function Calling Sequence

This section describes the standard function calling sequence, including stack frame layout, register usage, parameter passing and so on.

The standard calling sequence requirements apply only to global functions. Local functions that are not reachable from other compilation units may use different conventions. Nevertheless, it is recommended that all functions use the standard calling sequence when possible.

### 3.2.1 Registers and the Stack Frame

The AMD64 architecture provides 16 general purpose 64-bit registers. In addition the architecture provides 16 SSE registers, each 128 bits wide and 8 x87 floating point registers, each 80 bits wide. Each of the x87 floating point registers may be referred to in *MMX/*3DNow! mode as a 64-bit register. All of these registers are global to all procedures active for a given thread.

Intel AVX (Advanced Vector Extensions) provides 16 256-bit wide AVX registers (%ymm0 - %ymm15). The lower 128-bits of %ymm0 - %ymm15 are aliased to the respective 128b-bit SSE registers (%xmm0 - %xmm15). For purposes of parameter passing and function return, %xmmN and %ymmN refer to the same register. Only one of them can be used at the same time. We use vector register to refer to either SSE or AVX register.

This subsection discusses usage of each register. Registers %rbp, %rbx and %r12 through %r15 "belong" to the calling function and the called function is required to preserve their values. In other words, a called function must preserve these registers' values for its caller. Remaining registers "belong" to the called function.<sup>5</sup> If a calling function wants to preserve such a register value across a function call, it must save the value in its local stack frame.

The CPU shall be in x87 mode upon entry to a function. Therefore, every function that uses the *MMX* registers is required to issue an emms or femms instruction after using *MMX* registers, before returning or calling another function. The direction flag DF in the %rFLAGS register must be clear (set to "forward" direction) on function entry and return. Other user flags have no specified role in the standard calling sequence and are *not* preserved across calls.

The control bits of the MXCSR register are callee-saved (preserved across calls), while the status bits are caller-saved (not preserved). The x87 status word register is caller-saved, whereas the x87 control word is callee-saved.

<sup>&</sup>lt;sup>5</sup>Note that in contrast to the Intel386 ABI, %rdi, and %rsi belong to the called function, not the caller.

<sup>&</sup>lt;sup>6</sup>All x87 registers are caller-saved, so callees that make use of the *MMX* registers may use the faster femms instruction.

Figure 3.3: Stack Frame with Base Pointer

| Position    | Contents                    | Frame    |

|-------------|-----------------------------|----------|

| 8n+16(%rbp) | memory argument eightbyte n |          |

|             |                             | Previous |

| 16(%rbp)    | memory argument eightbyte 0 |          |

| 8(%rbp)     | return address              |          |

| 0(%rbp)     | previous %rbp value         |          |

| -8(%rbp)    | unspecified                 | Current  |

|             |                             |          |

| 0(%rsp)     | variable size               |          |

| -128(%rsp)  | red zone                    |          |

#### 3.2.2 The Stack Frame

In addition to registers, each function has a frame on the run-time stack. This stack grows downwards from high addresses. Figure 3.3 shows the stack organization.

The end of the input argument area shall be aligned on a 16 (32, if  $\__m256$  is passed on stack) byte boundary. In other words, the value (\$rsp + 8) is always a multiple of 16 (32) when control is transferred to the function entry point. The stack pointer, \$rsp, always points to the end of the latest allocated stack frame. <sup>7</sup>

The 128-byte area beyond the location pointed to by %rsp is considered to be reserved and shall not be modified by signal or interrupt handlers. Therefore, functions may use this area for temporary data that is not needed across function calls. In particular, leaf functions may use this area for their entire stack frame, rather than adjusting the stack pointer in the prologue and epilogue. This area is known as the red zone.

<sup>&</sup>lt;sup>7</sup>The conventional use of %rbp as a frame pointer for the stack frame may be avoided by using %rsp (the stack pointer) to index into the stack frame. This technique saves two instructions in the prologue and epilogue and makes one additional general-purpose register (%rbp) available.

<sup>&</sup>lt;sup>8</sup>Locations within 128 bytes can be addressed using one-byte displacements.

### 3.2.3 Parameter Passing

After the argument values have been computed, they are placed either in registers or pushed on the stack. The way how values are passed is described in the following sections.

**Definitions** We first define a number of classes to classify arguments. The classes are corresponding to AMD64 register classes and defined as:

- **INTEGER** This class consists of integral types that fit into one of the general purpose registers.

- **SSE** The class consists of types that fit into a vector register.

- **SSEUP** The class consists of types that fit into a vector register and can be passed and returned in the upper bytes of it.

- **X87, X87UP** These classes consists of types that will be returned via the x87 FPU.

- **COMPLEX\_X87** This class consists of types that will be returned via the x87 FPU

- **NO\_CLASS** This class is used as initializer in the algorithms. It will be used for padding and empty structures and unions.

- **MEMORY** This class consists of types that will be passed and returned in memory via the stack.

- **Classification** The size of each argument gets rounded up to eightbytes. The basic types are assigned their natural classes:

- Arguments of types (signed and unsigned) \_Bool, char, short, int, long, long long, and pointers are in the INTEGER class.

- Arguments of types float, double, \_Decimal32, \_Decimal64 and \_\_m64 are in class SSE.

<sup>&</sup>lt;sup>9</sup>Therefore the stack will always be eightbyte aligned.

- Arguments of types \_\_\_float128, \_Decimal128 and \_\_\_m128 are split into two halves. The least significant ones belong to class SSE, the most significant one to class SSEUP.

- Arguments of type \_\_\_m256 are split into four eightbyte chunks. The least significant one belongs to class SSE and all the others to class SSEUP.

- The 64-bit mantissa of arguments of type long double belongs to class X87, the 16-bit exponent plus 6 bytes of padding belongs to class X87UP.

- Arguments of type \_\_int128 offer the same operations as INTEGERs, yet they do not fit into one general purpose register but require two registers.

For classification purposes \_\_int128 is treated as if it were implemented as:

```

typedef struct {

long low, high;

} __int128;

```

with the exception that arguments of type \_\_int128 that are stored in memory must be aligned on a 16-byte boundary.

• Arguments of complex T where T is one of the types float or double are treated as if they are implemented as:

```

struct complexT {

T real;

T imag;

};

```

• A variable of type complex long double is classified as type COM-PLEX\_X87.

The classification of aggregate (structures and arrays) and union types works as follows:

1. If the size of an object is larger than four eightbytes, or it contains unaligned fields, it has class MEMORY <sup>10</sup>.

<sup>&</sup>lt;sup>10</sup>The post merger clean up described later ensures that, for the processors that do not support the \_\_m256 type, if the size of an object is larger than two eightbytes and the first eightbyte is not SSE or any other eightbyte is not SSEUP, it still has class MEMORY. This in turn ensures that for processors that do support the \_\_m256 type, if the size of an object is four eightbytes and the first eightbyte is SSE and all other eightbytes are SSEUP, it can be passed in a register.

- 2. If a C++ object has either a non-trivial copy constructor or a non-trivial destructor <sup>11</sup>, it is passed by invisible reference (the object is replaced in the parameter list by a pointer that has class INTEGER) <sup>12</sup>.

- 3. If the size of the aggregate exceeds a single eightbyte, each is classified separately. Each eightbyte gets initialized to class NO\_CLASS.

- 4. Each field of an object is classified recursively so that always two fields are considered. The resulting class is calculated according to the classes of the fields in the eightbyte:

- (a) If both classes are equal, this is the resulting class.

- (b) If one of the classes is NO\_CLASS, the resulting class is the other class.

- (c) If one of the classes is MEMORY, the result is the MEMORY class.

- (d) If one of the classes is INTEGER, the result is the INTEGER.

- (e) If one of the classes is X87, X87UP, COMPLEX\_X87 class, MEM-ORY is used as class.

- (f) Otherwise class SSE is used.

- 5. Then a post merger cleanup is done:

- (a) If one of the classes is MEMORY, the whole argument is passed in memory.

- (b) If X87UP is not preceded by X87, the whole argument is passed in memory.

- (c) If the size of the aggregate exceeds two eightbytes and the first eightbyte isn't SSE or any other eightbyte isn't SSEUP, the whole argument is passed in memory.

- its class has no virtual functions and no virtual base classes, and

- all the direct base classes of its class have trivial de/constructors, and

- for all the nonstatic data members of its class that are of class type (or array thereof), each such class has a trivial de/constructor.

<sup>&</sup>lt;sup>11</sup>A de/constructor is trivial if it is an implicitly-declared default de/constructor and if:

<sup>&</sup>lt;sup>12</sup>An object with either a non-trivial copy constructor or a non-trivial destructor cannot be passed by value because such objects must have well defined addresses. Similar issues apply when returning an object from a function.

(d) If SSEUP is not preceded by SSE or SSEUP, it is converted to SSE.

**Passing** Once arguments are classified, the registers get assigned (in left-to-right order) for passing as follows:

- 1. If the class is MEMORY, pass the argument on the stack.

- 2. If the class is INTEGER, the next available register of the sequence %rdi, %rsi, %rdx, %rcx, %r8 and %r9 is used<sup>13</sup>.

- 3. If the class is SSE, the next available vector register is used, the registers are taken in the order from %xmm0 to %xmm7.

- 4. If the class is SSEUP, the eightbyte is passed in the next available eightbyte chunk of the last used vector register.

- 5. If the class is X87, X87UP or COMPLEX\_X87, it is passed in memory.

When a value of type \_Bool is returned or passed in a register or on the stack, bit 0 contains the truth value and bits 1 to 7 shall be zero<sup>14</sup>.

If there are no registers available for any eightbyte of an argument, the whole argument is passed on the stack. If registers have already been assigned for some eightbytes of such an argument, the assignments get reverted.

Once registers are assigned, the arguments passed in memory are pushed on the stack in reversed (right-to-left<sup>15</sup>) order.

For calls that may call functions that use varargs or stdargs (prototype-less calls or calls to functions containing ellipsis (...) in the declaration) %al<sup>16</sup> is used as hidden argument to specify the number of vector registers used. The contents

<sup>&</sup>lt;sup>13</sup>Note that %r11 is neither required to be preserved, nor is it used to pass arguments. Making this register available as scratch register means that code in the PLT need not spill any registers when computing the address to which control needs to be transferred. %rax is used to indicate the number of vector arguments passed to a function requiring a variable number of arguments. %r10 is used for passing a function's static chain pointer.

<sup>&</sup>lt;sup>14</sup>Other bits are left unspecified, hence the consumer side of those values can rely on it being 0 or 1 when truncated to 8 bit.

<sup>&</sup>lt;sup>15</sup>Right-to-left order on the stack makes the handling of functions that take a variable number of arguments simpler. The location of the first argument can always be computed statically, based on the type of that argument. It would be difficult to compute the address of the first argument if the arguments were pushed in left-to-right order.

<sup>&</sup>lt;sup>16</sup>Note that the rest of %rax is undefined, only the contents of %al is defined.

Figure 3.4: Register Usage

| Register    | Usage                                                                      | Preserved across function calls |

|-------------|----------------------------------------------------------------------------|---------------------------------|

| %rax        | temporary register; with variable arguments                                | No                              |

|             | passes information about the number of vector                              |                                 |

|             | registers used; 1 <sup>st</sup> return register                            |                                 |

| %rbx        | callee-saved register                                                      | Yes                             |

| %rcx        | used to pass 4 <sup>th</sup> integer argument to functions                 | No                              |

| %rdx        | used to pass 3 <sup>rd</sup> argument to functions; 2 <sup>nd</sup> return | No                              |

|             | register                                                                   |                                 |

| %rsp        | stack pointer                                                              | Yes                             |

| %rbp        | callee-saved register; optionally used as frame                            | Yes                             |

| -           | pointer                                                                    |                                 |

| %rsi        | used to pass 2 <sup>nd</sup> argument to functions                         | No                              |

| %rdi        | used to pass 1st argument to functions                                     | No                              |

| %r8         | used to pass 5 <sup>th</sup> argument to functions                         | No                              |

| %r9         | used to pass 6 <sup>th</sup> argument to functions                         | No                              |

| %r10        | temporary register, used for passing a function's                          | No                              |

|             | static chain pointer                                                       |                                 |

| %r11        | temporary register                                                         | No                              |

| %r12-r14    | callee-saved registers                                                     | Yes                             |

| %r15        | callee-saved register; optionally used as GOT                              | Yes                             |

|             | base pointer                                                               |                                 |

| %xmm0-%xmm1 | used to pass and return floating point arguments                           | No                              |

| %xmm2-%xmm7 | used to pass floating point arguments                                      | No                              |

| xmm8-xmm15  | temporary registers                                                        | No                              |

| %mmx0-%mmx7 | temporary registers                                                        | No                              |

| %st0,%st1   | temporary registers; used to return long                                   | No                              |

|             | double arguments                                                           |                                 |

| %st2-%st7   | temporary registers                                                        | No                              |

| %fs         | Reserved for system (as thread specific data reg-                          | No                              |

|             | ister)                                                                     |                                 |

| mxcsr       | SSE2 control and status word                                               | partial                         |

| x87 SW      | x87 status word                                                            | No                              |

| x87 CW      | x87 control word                                                           | Yes                             |

of %al do not need to match exactly the number of registers, but must be an upper bound on the number of vector registers used and is in the range 0–8 inclusive.

When passing \_\_m256 arguments to functions that use varargs or stdarg, function prototypes must be provided. Otherwise, the run-time behavior is undefined.

**Returning of Values** The returning of values is done according to the following algorithm:

- 1. Classify the return type with the classification algorithm.

- 2. If the type has class MEMORY, then the caller provides space for the return value and passes the address of this storage in %rdi as if it were the first argument to the function. In effect, this address becomes a "hidden" first argument. This storage must not overlap any data visible to the callee through other names than this argument.

- On return %rax will contain the address that has been passed in by the caller in %rdi.

- 3. If the class is INTEGER, the next available register of the sequence %rax, %rdx is used.

- 4. If the class is SSE, the next available vector register of the sequence %xmm0, %xmm1 is used.

- 5. If the class is SSEUP, the eightbyte is returned in the next available eightbyte chunk of the last used vector register.

- 6. If the class is X87, the value is returned on the X87 stack in %st0 as 80-bit x87 number.

- 7. If the class is X87UP, the value is returned together with the previous X87 value in %st0.

- 8. If the class is COMPLEX\_X87, the real part of the value is returned in %st0 and the imaginary part in %st1.

As an example of the register passing conventions, consider the declarations and the function call shown in Figure 3.5. The corresponding register allocation

is given in Figure 3.6, the stack frame offset given shows the frame before calling the function.

Figure 3.5: Parameter Passing Example

Figure 3.6: Register Allocation Example

| General Purpose Registers | Floating Point Registers | Stack Frame Offset |

|---------------------------|--------------------------|--------------------|

|---------------------------|--------------------------|--------------------|

| %rdi: | е       | %xmm0: | s.d | 0:  | ld |

|-------|---------|--------|-----|-----|----|

| %rsi: | f       | %xmm1: | m   | 16: | j  |

| %rdx: | s.a,s.b | %ymm2: | У   | 24: | k  |

| %rcx: | g       | %xmm3: | n   |     |    |

| %r8:  | h       |        |     |     |    |

| %r9:  | i       |        |     |     |    |

|       |         |        |     |     |    |

## 3.3 Operating System Interface

### 3.3.1 Exception Interface

As the AMD64 manuals describe, the processor changes mode to handle *exceptions*, which may be synchronous, floating-point/coprocessor or asynchronous. Synchronous and floating-point/coprocessor exceptions, being caused by instruction execution, can be explicitly generated by a process. This section, therefore, specifies those exception types with defined behavior. The AMD64 architecture classifies exceptions as *faults*, *traps*, and *aborts*. See the Intel386 ABI for more information about their differences.

#### **Hardware Exception Types**

The operating system defines the correspondence between hardware exceptions and the signals specified by signal (BA\_OS) as shown in table 3.1. Contrary to the i386 architecture, the AMD64 does not define any instructions that generate a bounds check fault in long mode.

### 3.3.2 Virtual Address Space

Processes begin with three logical segments, commonly called text, data, and stack. Use of shared libraries add other segments and a process may dynamically create segments.

## 3.3.3 Page Size

Systems are permitted to use any power-of-two page size between 4KB and 64KB, inclusive.

## 3.3.4 Virtual Address Assignments

Conceptually processes have the full address space available. In practice, however, several factors limit the size of a process.

<sup>&</sup>lt;sup>17</sup>0x0000ffff ffffffff is not a canonical address and cannot be used.

Table 3.1: Hardware Exceptions and Signals

| Number | Exception name                 | Signal  |

|--------|--------------------------------|---------|

| 0      | divide error fault             | SIGFPE  |

| 1      | single step trap/fault         | SIGTRAP |

| 2      | non-maskable interrupt         | none    |

| 3      | breakpoint trap                | SIGTRAP |

| 4      | overflow trap                  | SIGSEGV |

| 5      | (reserved)                     |         |

| 6      | invalid opcode fault           | SIGILL  |

| 7      | no coprocessor fault           | SIGFPE  |

| 8      | double fault abort             | none    |

| 9      | coprocessor overrun abort      | SIGSEGV |

| 10     | invalid TSS fault              | none    |

| 11     | segment no present fault       | none    |

| 12     | stack exception fault          | SIGSEGV |

| 13     | general protection fault/abort | SIGSEGV |

| 14     | page fault                     | SIGSEGV |

| 15     | (reserved)                     |         |

| 16     | coprocessor error fault        | SIGFPE  |

| other  | (unspecified)                  | SIGILL  |

Table 3.2: Floating-Point Exceptions

| Code       | Reason                           |  |  |

|------------|----------------------------------|--|--|

| FPE_FLTDIV | floating-point divide by zero    |  |  |

| FPE_FLTOVF | floating-point overflow          |  |  |

| FPE_FLTUND | floating-point underflow         |  |  |

| FPE_FLTRES | floating-point inexact result    |  |  |

| FPE_FLTINV | invalid floating-point operation |  |  |

- The system reserves a configuration dependent amount of virtual space.

- The system reserves a configuration dependent amount of space per process.

- A process whose size exceeds the system's available combined physical memory and secondary storage cannot run. Although some physical memory must be present to run any process, the system can execute processes that are bigger than physical memory, paging them to and from secondary storage. Nonetheless, both physical memory and secondary storage are shared resources. System load, which can vary from one program execution to the next, affects the available amount.

Programs that dereference null pointers are erroneous and a process should not expect 0x0 to be a valid address.

Figure 3.7: Virtual Address Configuration

Although applications may control their memory assignments, the typical arrangement appears in figure 3.8.

Figure 3.8: Conventional Segment Arrangements

## 3.4 Process Initialization

## 3.4.1 Initial Stack and Register State

### **Special Registers**

The AMD64 architecture defines floating point instructions. At process startup the two floating point units, SSE2 and x87, both have all floating-point exception status flags cleared. The status of the control words is as defined in tables 3.3 and 3.4.

Table 3.3: x87 Floating-Point Control Word

| Field | Value | Note                      |

|-------|-------|---------------------------|

| RC    | 0     | Round to nearest          |

| PC    | 11    | Double extended precision |

| PM    | 1     | Precision masked          |

| UM    | 1     | Underflow masked          |

| OM    | 1     | Overflow masked           |

| ZM    | 1     | Zero divide masked        |

| DM    | 1     | De-normal operand masked  |

| IM    | 1     | Invalid operation masked  |

Table 3.4: MXCSR Status Bits

| Field | Value | Note                     |

|-------|-------|--------------------------|

| FZ    | 0     | Do not flush to zero     |

| RC    | 0     | Round to nearest         |

| PM    | 1     | Precision masked         |

| UM    | 1     | Underflow masked         |

| OM    | 1     | Overflow masked          |

| ZM    | 1     | Zero divide masked       |

| DM    | 1     | De-normal operand masked |

| IM    | 1     | Invalid operation masked |

| DAZ   | 0     | De-normals are not zero  |

The rFLAGS register contains the system flags, such as the direction flag and the carry flag. The low 16 bits (FLAGS portion) of rFLAGS are accessible by application software. The state of them at process initialization is shown in table 3.5.

Table 3.5: rFLAGS Bits

| Field | Value | Note                 |

|-------|-------|----------------------|

| DF    | 0     | Direction forward    |

| CF    | 0     | No carry             |

| PF    | 0     | Even parity          |

| AF    | 0     | No auxiliary carry   |

| ZF    | 0     | No zero result       |

| SF    | 0     | Unsigned result      |

| OF    | 0     | No overflow occurred |

#### **Stack State**

This section describes the machine state that <code>exec</code> (BA\_OS) creates for new processes. Various language implementations transform this initial program state to the state required by the language standard.

For example, a C program begins executing at a function named main declared as:

```

extern int main ( int argc , char *argv[ ] , char* envp[ ] );

where

```

argc is a non-negative argument count

argv is an array of argument strings, with argv[argc] == 0

**envp** is an array of environment strings, terminated by a null pointer.

When main() returns its value is passed to exit() and if that has been over-ridden and returns, \_exit() (which must be immune to user interposition).

The initial state of the process stack, i.e. when \_start is called is shown in figure 3.9.

Figure 3.9: Initial Process Stack

| Purpose                            | Start Address  | Length            |

|------------------------------------|----------------|-------------------|

| Unspecified                        | High Addresses |                   |

| Information block, including argu- |                | varies            |

| ment strings, environment strings, |                |                   |

| auxiliary information              |                |                   |

| Unspecified                        |                |                   |

| Null auxiliary vector entry        |                | 1 eightbyte       |

| Auxiliary vector entries           |                | 2 eightbytes each |

| 0                                  |                | eightbyte         |

| Environment pointers               |                | 1 eightbyte each  |

| 0                                  | 8+8*argc+%rsp  | eightbyte         |

| Argument pointers                  | 8+%rsp         | argc eightbytes   |

| Argument count                     | %rsp           | eightbyte         |

| Undefined                          | Low Addresses  |                   |

Argument strings, environment strings, and the auxiliary information appear in no specific order within the information block and they need not be compactly allocated.

Only the registers listed below have specified values at process entry:

- **%rbp** The content of this register is unspecified at process initialization time, but the user code should mark the deepest stack frame by setting the frame pointer to zero.

- **%rsp** The stack pointer holds the address of the byte with lowest address which is part of the stack. It is guaranteed to be 16-byte aligned at process entry.

**%rdx** a function pointer that the application should register with atexit (BA\_OS).

It is unspecified whether the data and stack segments are initially mapped with execute permissions or not. Applications which need to execute code on the stack or data segments should take proper precautions, e.g., by calling mprotect().

#### 3.4.2 Thread State

New threads inherit the floating-point state of the parent thread and the state is private to the thread thereafter.

### 3.4.3 Auxiliary Vector

The auxiliary vector is an array of the following structures (ref. figure 3.10), interpreted according to the a\_type member.

Figure 3.10: auxv\_t Type Definition

```

typedef struct

{

int a_type;

union {

long a_val;

void *a_ptr;

void (*a_fnc)();

} a_un;

} auxv_t;

```

The AMD64 ABI uses the auxiliary vector types defined in figure 3.11.

Figure 3.11: Auxiliary Vector Types

| Name      | Value | a_un    |

|-----------|-------|---------|

| AT_NULL   | 0     | ignored |

| AT_IGNORE | 1     | ignored |

| AT_EXECFD | 2     | a_val   |

| AT_PHDR   | 3     | a_ptr   |

| AT_PHENT  | 4     | a_val   |

| AT_PHNUM  | 5     | a_val   |

| AT_PAGESZ | 6     | a_val   |

| AT_BASE   | 7     | a_ptr   |

| AT_FLAGS  | 8     | a_val   |

| AT_ENTRY  | 9     | a_ptr   |

| AT_NOTELF | 10    | a_val   |

| AT_UID    | 11    | a_val   |

| AT_EUID   | 12    | a_val   |

| AT_GID    | 13    | a_val   |

| AT_EGID   | 14    | a_val   |

- **AT\_NULL** The auxiliary vector has no fixed length; instead its last entry's a\_type member has this value.

- **AT\_IGNORE** This type indicates the entry has no meaning. The corresponding value of a\_un is undefined.

- AT\_EXECFD At process creation the system may pass control to an interpreter program. When this happens, the system places either an entry of type AT\_EXECFD or one of type AT\_PHDR in the auxiliary vector. The entry for type AT\_EXECFD uses the a\_val member to contain a file descriptor open to read the application program's object file.

- AT\_PHDR The system may create the memory image of the application program before passing control to the interpreter program. When this happens, the a\_ptr member of the AT\_PHDR entry tells the interpreter where to find the program header table in the memory image.

- **AT\_PHENT** The a\_val member of this entry holds the size, in bytes, of one entry in the program header table to which the AT\_PHDR entry points.

- **AT\_PHNUM** The a\_val member of this entry holds the number of entries in the program header table to which the AT\_PHDR entry points.

- **AT\_PAGESZ** If present, this entry's a\_val member gives the system page size, in bytes.

- **AT\_BASE** The a\_ptr member of this entry holds the base address at which the interpreter program was loaded into memory. See "Program Header" in the System V ABI for more information about the base address.

- **AT\_FLAGS** If present, the a\_val member of this entry holds one-bit flags. Bits with undefined semantics are set to zero.

- **AT\_ENTRY** The a\_ptr member of this entry holds the entry point of the application program to which the interpreter program should transfer control.

- **AT\_NOTELF** The a\_val member of this entry is non-zero if the program is in another format than ELF.

- **AT\_UID** The a\_val member of this entry holds the real user id of the process.

- **AT\_EUID** The a\_val member of this entry holds the effective user id of the process.

- **AT\_GID** The a\_val member of this entry holds the real group id of the process.

- **AT\_EGID** The a\_val member of this entry holds the effective group id of the process.

## 3.5 Coding Examples

This section discusses example code sequences for fundamental operations such as calling functions, accessing static objects, and transferring control from one part of a program to another. Unlike previous material, this material is not normative.

#### 3.5.1 Architectural Constraints

The AMD64 architecture usually does not allow an instruction to encode arbitrary 64-bit constants as immediate operand. Most instructions accept 32-bit immediates that are sign extended to the 64-bit ones. Additionally the 32-bit operations with register destinations implicitly perform zero extension making loads of 64-bit immediates with upper half set to 0 even cheaper.

Additionally the branch instructions accept 32-bit immediate operands that are sign extended and used to adjust the instruction pointer. Similarly an instruction pointer relative addressing mode exists for data accesses with equivalent limitations.

In order to improve performance and reduce code size, it is desirable to use different code models depending on the requirements.

Code models define constraints for symbolic values that allow the compiler to generate better code. Basically code models differ in addressing (absolute versus position independent), code size, data size and address range. We define only a small number of code models that are of general interest:

**Small code model** The virtual address of code executed is known at link time. Additionally all symbols are known to be located in the virtual addresses in the range from 0 to  $2^{31} - 2^{24} - 1$  or from 0x00000000 to  $0x7effffff^{18}$ .

This allows the compiler to encode symbolic references with offsets in the range from  $-(2^{31})$  to  $2^{24}$  or from 0x80000000 to 0x01000000 directly in the sign extended immediate operands, with offsets in the range from 0 to  $2^{31}-2^{24}$  or from 0x00000000 to 0x7f000000 in the zero extended immediate operands and use instruction pointer relative addressing for the symbols with offsets in the range  $-(2^{24})$  to  $2^{24}$  or 0xff000000 to 0x01000000.

This is the fastest code model and we expect it to be suitable for the vast majority of programs.

**Kernel code model** The kernel of an operating system is usually rather small but runs in the negative half of the address space. So we define all symbols to be in the range from  $2^{64} - 2^{31}$  to  $2^{64} - 2^{24}$  or from 0xfffffffff80000000 to 0xfffffffff0000000.

$<sup>^{18}</sup>$  The number 24 is chosen arbitrarily. It allows for all memory of objects of size up to  $2^{24}$  or 16M bytes to be addressed directly because the base address of such objects is constrained to be less than  $2^{31}-2^{24}$  or 0x7f000000. Without such constraint only the base address would be accessible directly, but not any offsetted variant of it.

This code model has advantages similar to those of the small model, but allows encoding of zero extended symbolic references only for offsets from  $2^{31}$  to  $2^{31} + 2^{24}$  or from 0x80000000 to 0x81000000. The range offsets for sign extended reference changes to 0 to  $2^{31} + 2^{24}$  or 0x00000000 to 0x81000000.

Medium code model In the medium model, the data section is split into two parts — the data section still limited in the same way as in the small code model and the large data section having no limits except for available addressing space. The program layout must be set in a way so that large data sections (.ldata, .lrodata, .lbss) come after the text and data sections.

This model requires the compiler to use movabs instructions to access large static data and to load addresses into registers, but keeps the advantages of the small code model for manipulation of addresses in the small data and text sections (specially needed for branches).

By default only data larger than 65535 bytes will be placed in the large data section.

**Large code model** The large code model makes no assumptions about addresses and sizes of sections.

The compiler is required to use the movabs instruction, as in the medium code model, even for dealing with addresses inside the text section. Additionally, indirect branches are needed when branching to addresses whose offset from the current instruction pointer is unknown.

It is possible to avoid the limitation on the text section in the small and medium models by breaking up the program into multiple shared libraries, so this model is strictly only required if the text of a single function becomes larger than what the medium model allows.

**Small position independent code model (PIC)** Unlike the previous models, the virtual addresses of instructions and data are not known until dynamic link time. So all addresses have to be relative to the instruction pointer.

Additionally the maximum distance between a symbol and the end of an instruction is limited to  $2^{31}-2^{24}-1$  or 0x7effffff, allowing the compiler to use instruction pointer relative branches and addressing modes supported

by the hardware for every symbol with an offset in the range  $-(2^{24})$  to  $2^{24}$  or 0xff000000 to 0x01000000.

**Medium position independent code model (PIC)** This model is like the previous model, but similarly to the medium static model adds large data sections at the end of object files.

In the medium PIC model, the instruction pointer relative addressing can not be used directly for accessing large static data, since the offset can exceed the limitations on the size of the displacement field in the instruction. Instead an unwind sequence consisting of movabs, lea and add needs to be used.

**Large position independent code model (PIC)** This model is like the previous model, but makes no assumptions about the distance of symbols.

The large PIC model implies the same limitation as the medium PIC model regarding addressing of static data. Additionally, references to the global offset table and to the procedure linkage table and branch destinations need to be calculated in a similar way. Further the size of the text segment is allowed to be up to 16EB in size, hence similar restrictions apply to all address references into the text segments, including branches.

#### 3.5.2 Conventions

In this document some special assembler symbols are used in the coding examples and discussion. They are:

- name@GOT: specifies the offset to the GOT entry for the symbol name from the base of the GOT.

- name@GOTPLT: specifies the offset to the GOT entry for the symbol name from the base of the GOT, implying that there is a corresponding PLT entry.

- name@GOTOFF: specifies the offset to the location of the symbol name from the base of the GOT.

- name@GOTPCREL: specifies the offset to the GOT entry for the symbol name from the current code location.

- name@PLT: specifies the offset to the PLT entry of symbol name from the current code location.

- name@PLTOFF: specifies the offset to the PLT entry of symbol name from the base of the GOT.

- \_GLOBAL\_OFFSET\_TABLE\_: specifies the offset to the base of the GOT from the current code location.

## 3.5.3 Position-Independent Function Prologue

In the small code model all addresses (including GOT entries) are accessible via the IP-relative addressing provided by the AMD64 architecture. Hence there is no need for an explicit GOT pointer and therefore no function prologue for setting it up is necessary.

In the medium and large code models a register has to be allocated to hold the address of the GOT in position-independent objects, because the AMD64 ISA does not support an immediate displacement larger than 32 bits.

As %r15 is preserved across function calls, it is initialized in the function prolog to hold the GOT address<sup>19</sup> for non-leaf functions which call other functions through the PLT. Other functions are free to use any other register. Throughout this document, %r15 will be used in examples.

Figure 3.12: Position-Independent Function Prolog Code medium model:

leaq

```

large model:

pushq %r15  # save %r15

leaq 1f(%rip),%r11  # absolute %rip

1: movabs $_GLOBAL_OFFSET_TABLE_,%r15  # offset to the GOT (R_X86_64_GOTPC64)

leaq (%r11,%r15),%r15  # absolute address of the GOT

```

\_GLOBAL\_OFFSET\_TABLE\_(%rip), %r15 # GOTPC32 reloc